RISC-V® Debugger & Trace

Any RISC-V Core in Any Chip

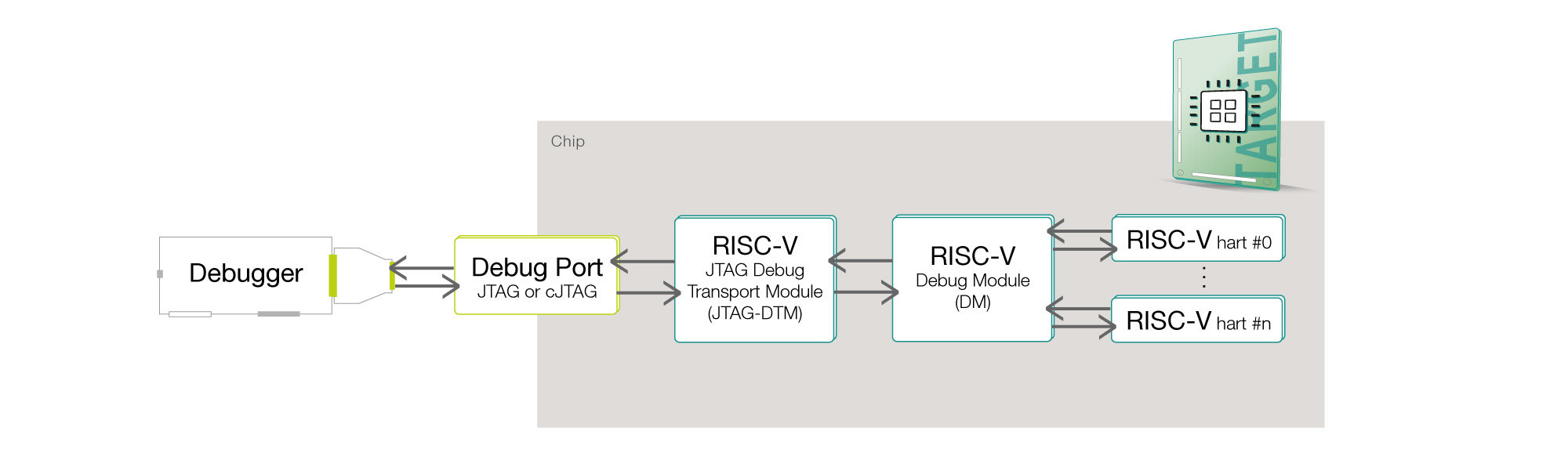

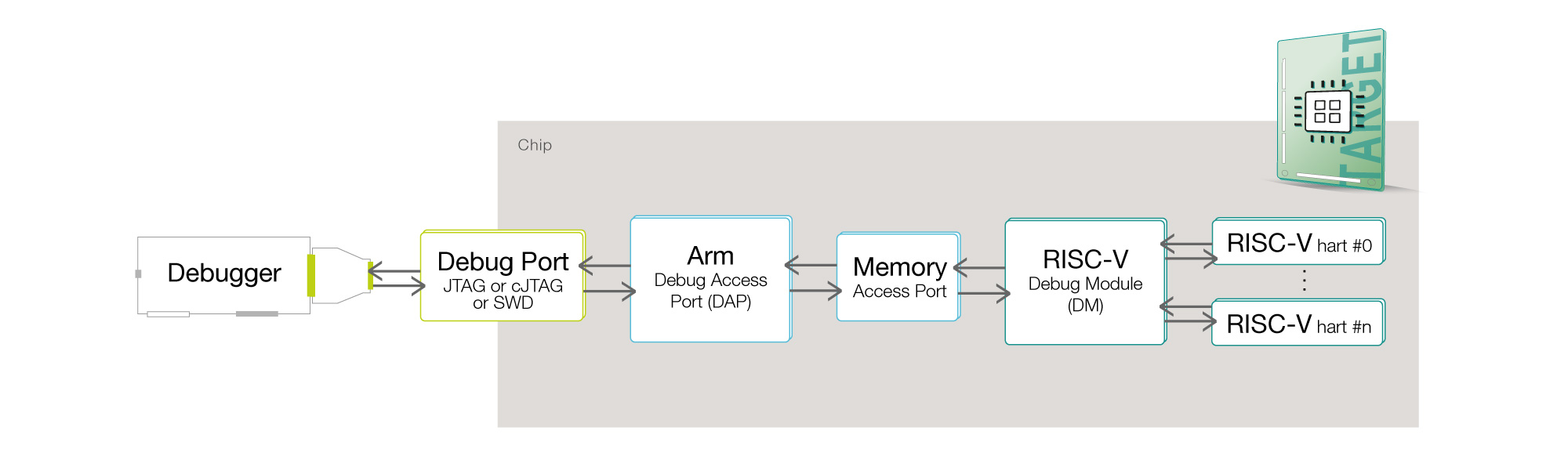

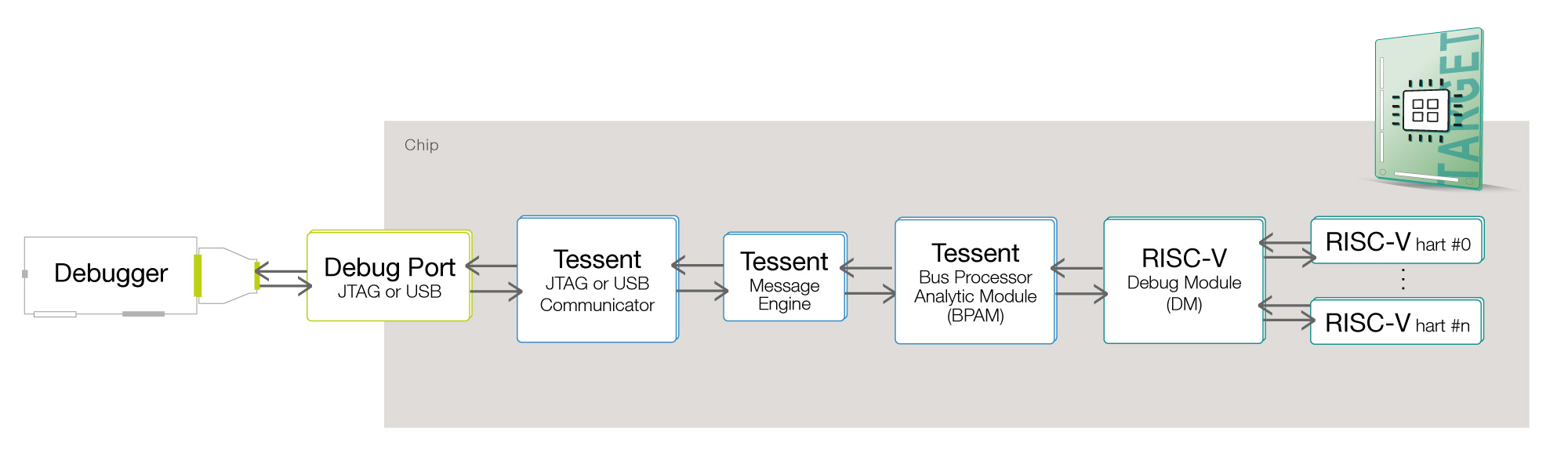

Analyze any design implementing the RISC-V Instruction Set Architecture (ISA), from a single tiny microcontroller using an RV32, to a massive multicore application processor, that uses the RV64 with our leading edge development tools.

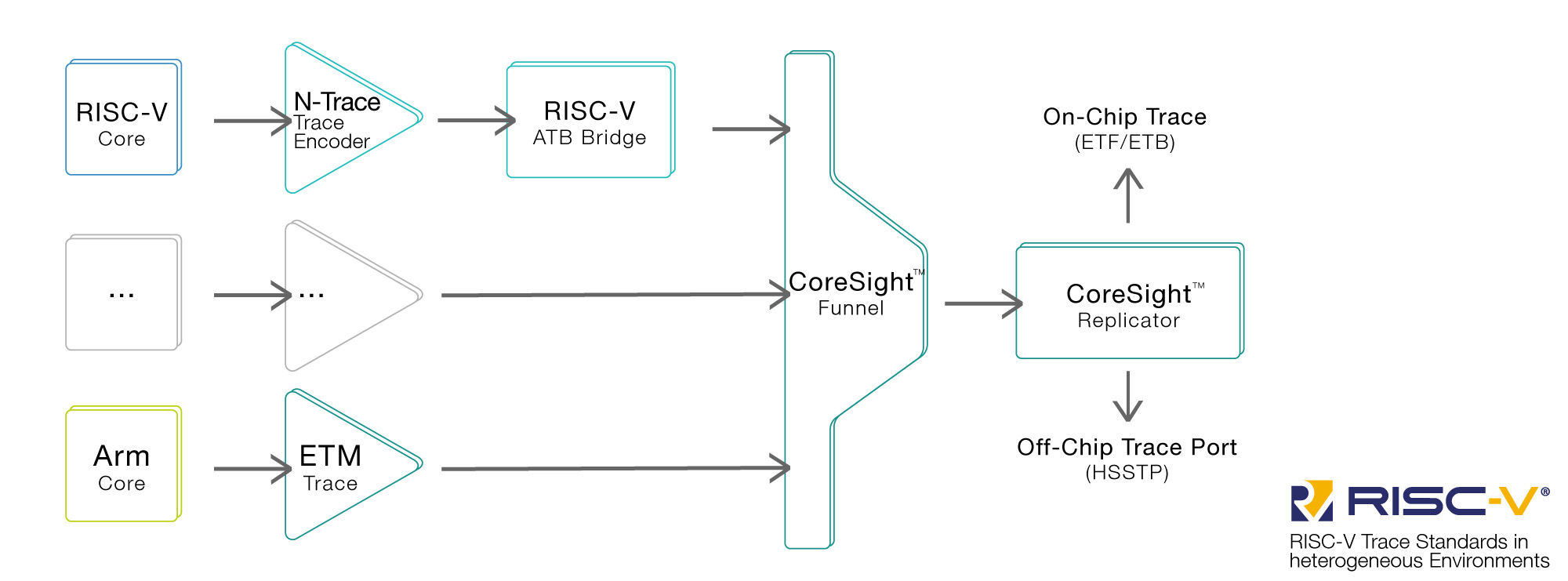

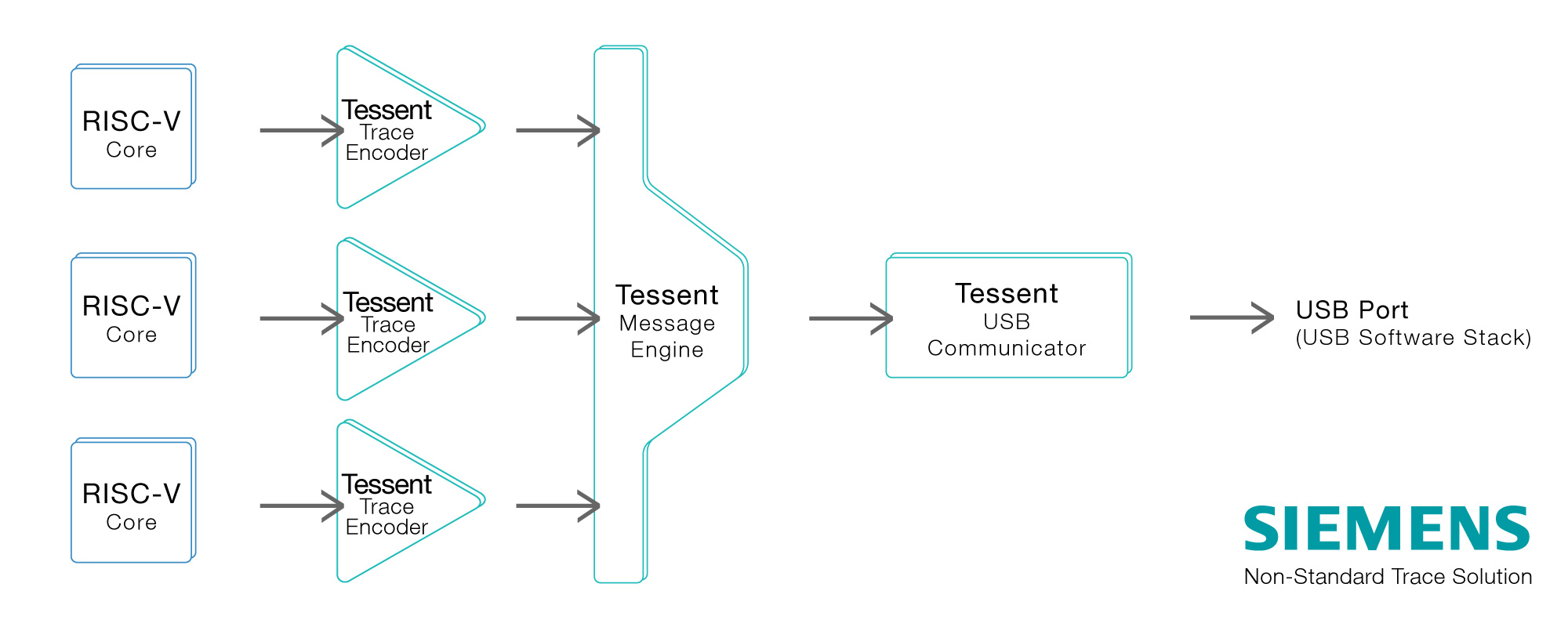

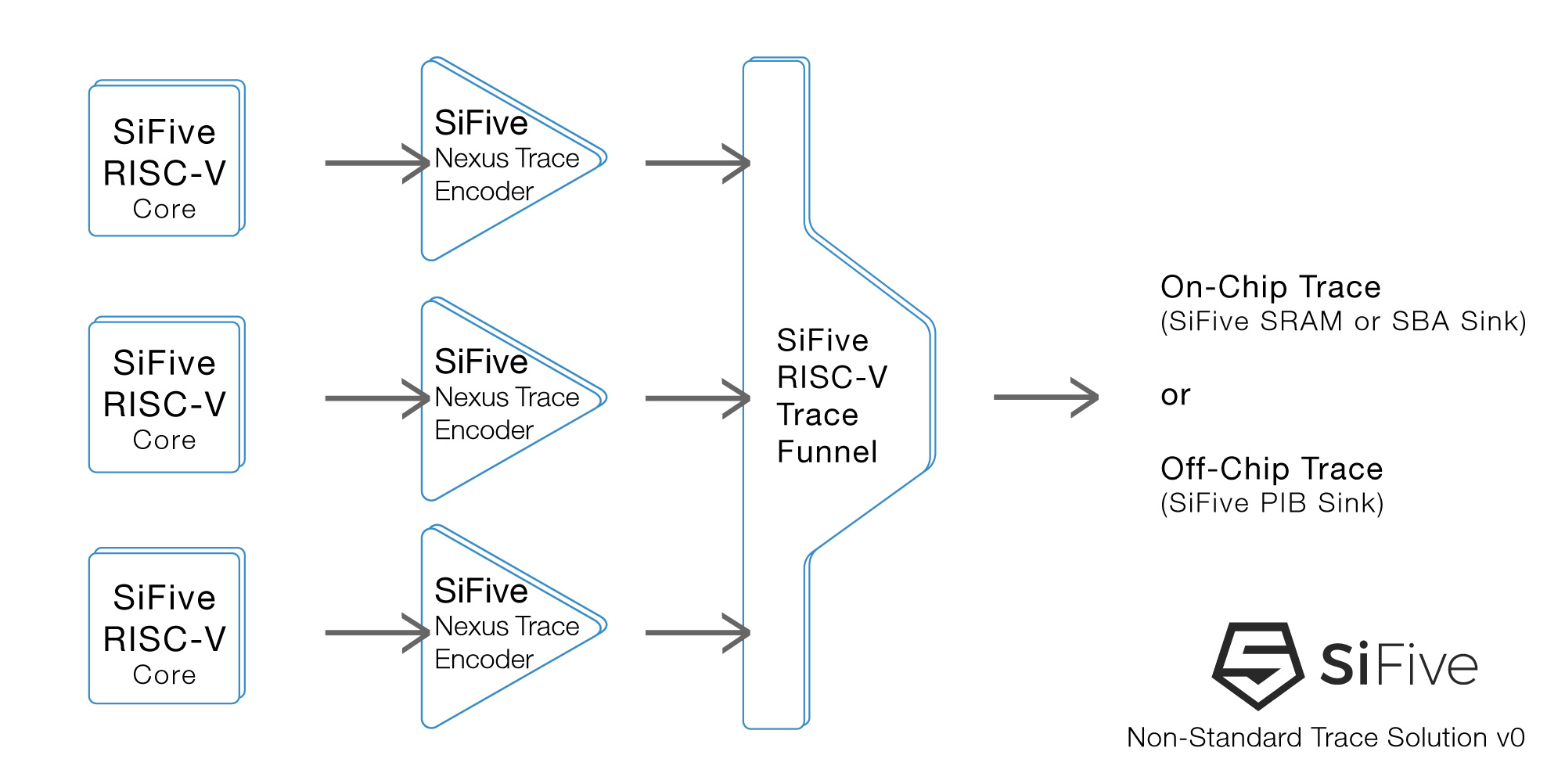

Using our TRACE32® tools you can debug and control any RISC-V core (along with all of the other cores) in any SoC via a single debug interface, all at the same time. TRACE32® tools support real-time on- and off-chip tracing for all major RISC-V trace systems.

From the beginning we have been a strategic member of the RISC-V foundation, supporting nearly all today’s chips implementing the RISC-V ISA. Thanks to the long-standing close partnership with RISC-V processor designers and semiconductor manufacturers, future chip developments enabled by us from the very beginning – ensuring your future-proof investment.

Supported Sub-Architectures

RISC-V 32bit/64bit, AndesCore™ V5, ARC-V™, MicroBlaze™ V, Nios® V, SiFive® Core IP

Utilize All Debug Features for All RISC-V ISA Extensions

By using our powerful debug modules you can apply our full debug feature set to any RISC-V core design including all ISA extensions like floating point, compressed instructions, vector arithmetic, atomic instructions, integer multiplication and even custom ISA extensions. Utilize full on-chip breakpoint support, run-time memory access, flash programming and benchmark counters. Everything is scriptable, which enables you to automate tests very easily.

Learn more about our debug systemWhich RISC-V core do you want to use?

Check out our catalogue of predefined solutions and find the ideal toolset for your project.

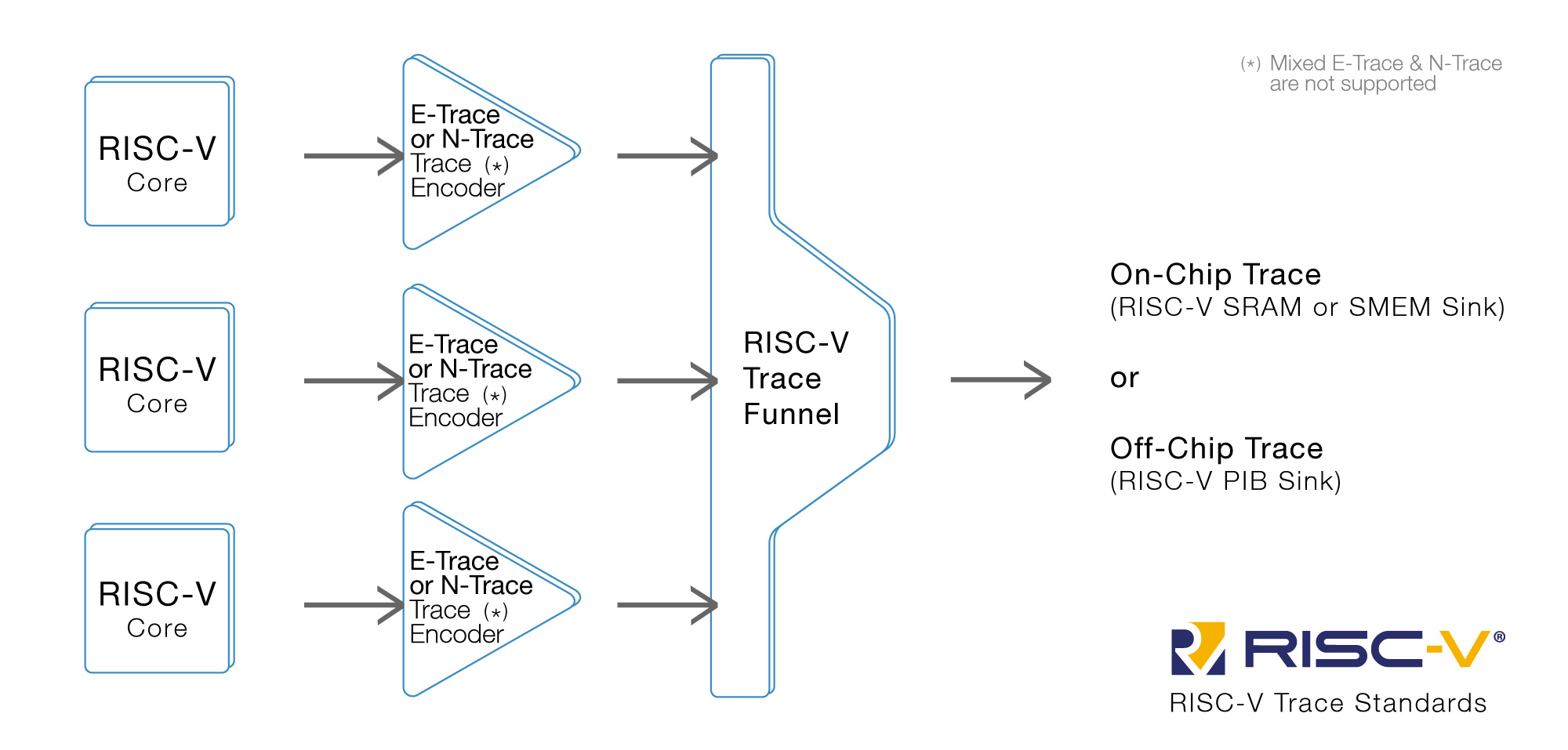

Capture Your Core Actions on Each RISC-V Chip

Stop mode debugging can be a powerful tool but tracing is even better. Our trace solutions for RISC-V support both on-chip trace for various technologies as well as the much more powerful off-chip trace, which can save the trace data inside the target memory or emit it to one of our PowerTrace tools.

Which RISC-V core do you want to use?

Check out our catalogue of predefined solutions and find the ideal toolset for your project.

Get Ready Before Your Silicon is

Test your RISC-V code in your custom SoC before your SoC is ready. Taping out your SoC takes a lot of time, but TRACE32 allows you to start software development on virtual prototypes and simulators, using the same GUI and toolset that you would use later with the real chip. To some extent it is also possible to verify the debug interface of your individual SoC before starting the taping out.

3rd Party Tools Supported for RISC-V

The following features are available for all architectures supported by TRACE32. Please contact us if your device or tool is not listed here; support is often already on its way.