Debug and Trace AMD Zynq™ UltraScale+™ MPSoC

Heterogeneous Multiprocessing Platform for Broad Range of Embedded Applications.

Implements:

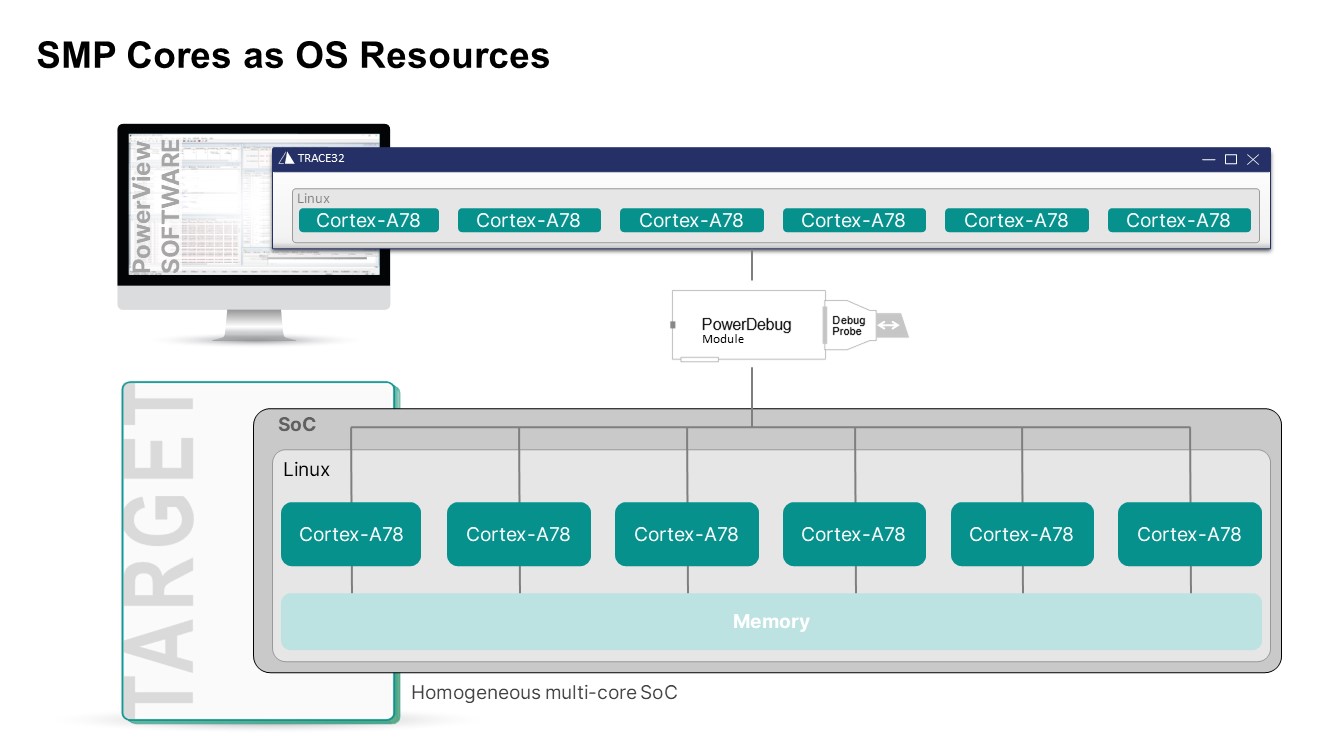

- 4 x Application Cores Arm® Cortex®-A53

- 2 x Real-Time Cores Arm® Cortex®-R5F.

- 1 x Platform Management Unit MicroBlaze Hard-IP.

- Optional Arm® Cortex®-M3, Cortex®-M1 and MicroBlaze Soft-Cores in the FPGA Logic.

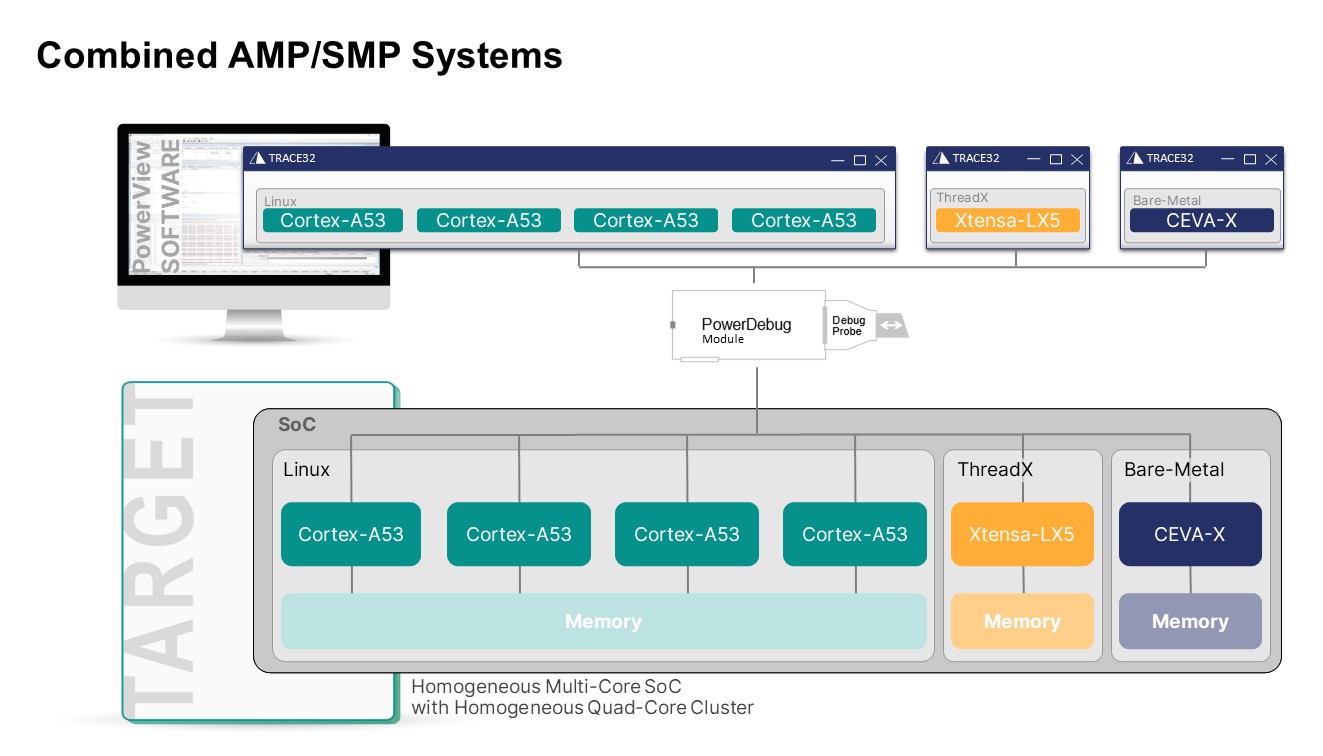

The application cores are typically configured as an SMP cluster running a rich OS like Linux, while the other cores usually operate asynchronously.

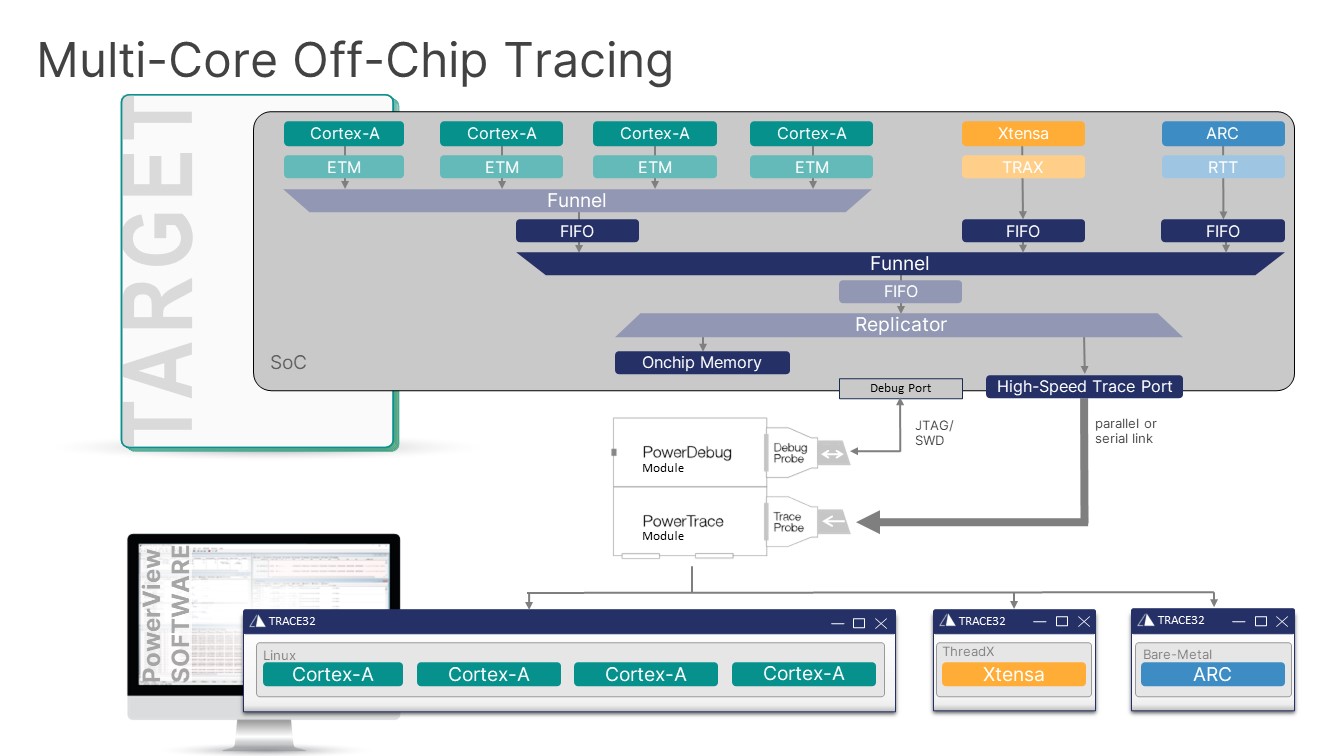

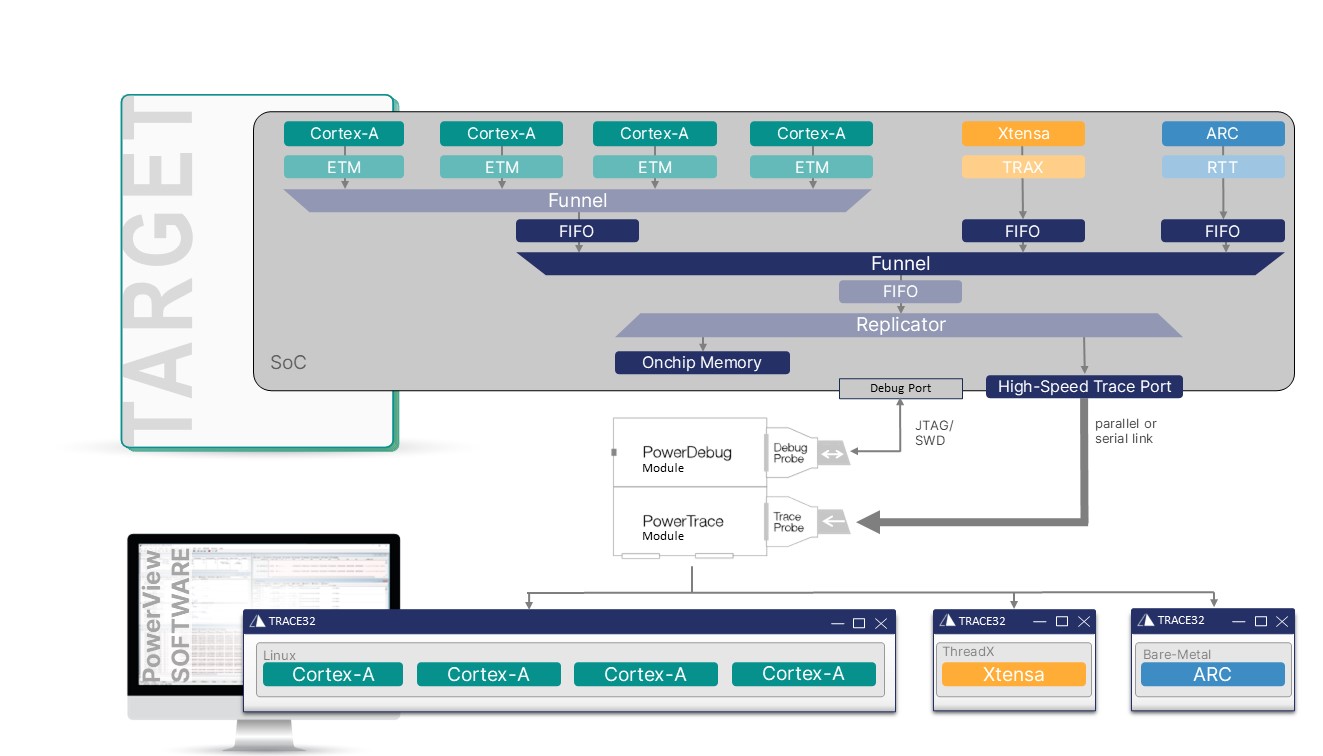

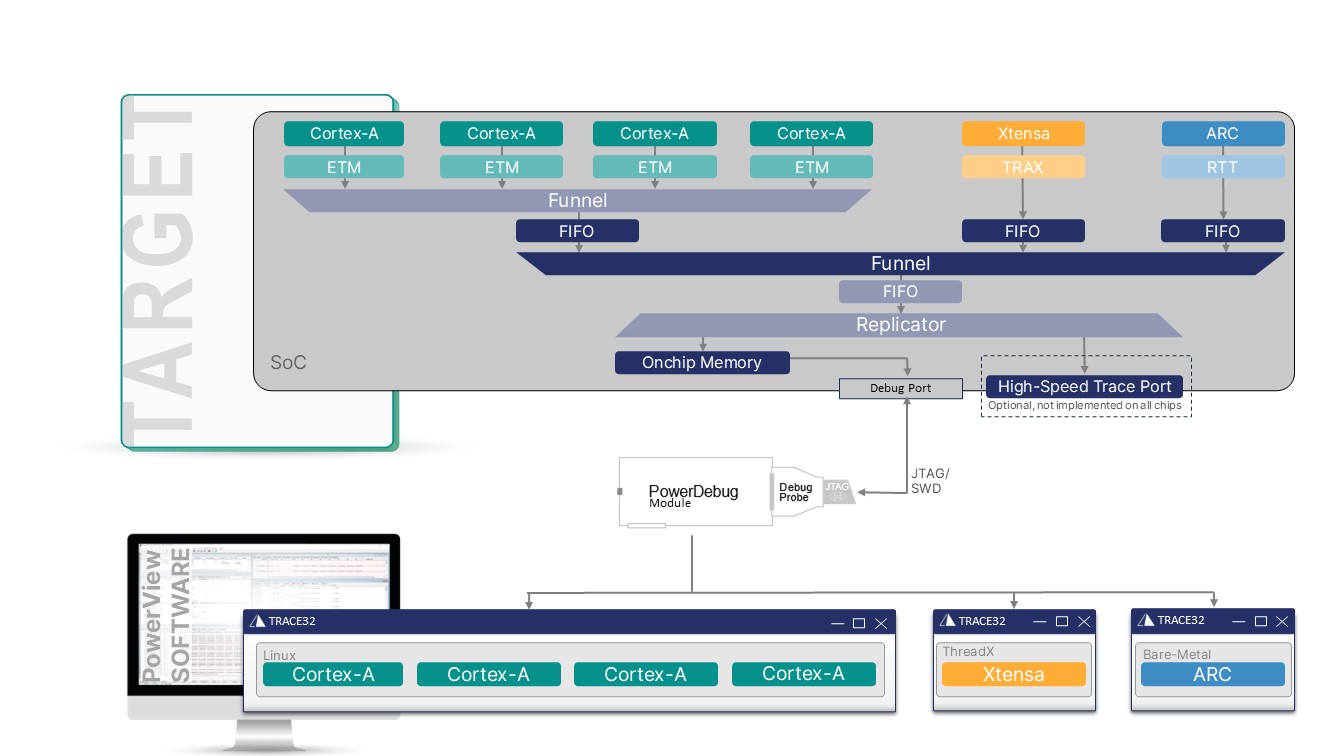

Our TRACE32® tools can debug all cores concurrently. You can trace the Cortex-A and Cortex-R cores via parallel or serial Off-Chip-Trace or via On-Chip-Buffers.