TriCore™ Debugger & Trace

Total TriCore Debug and Trace

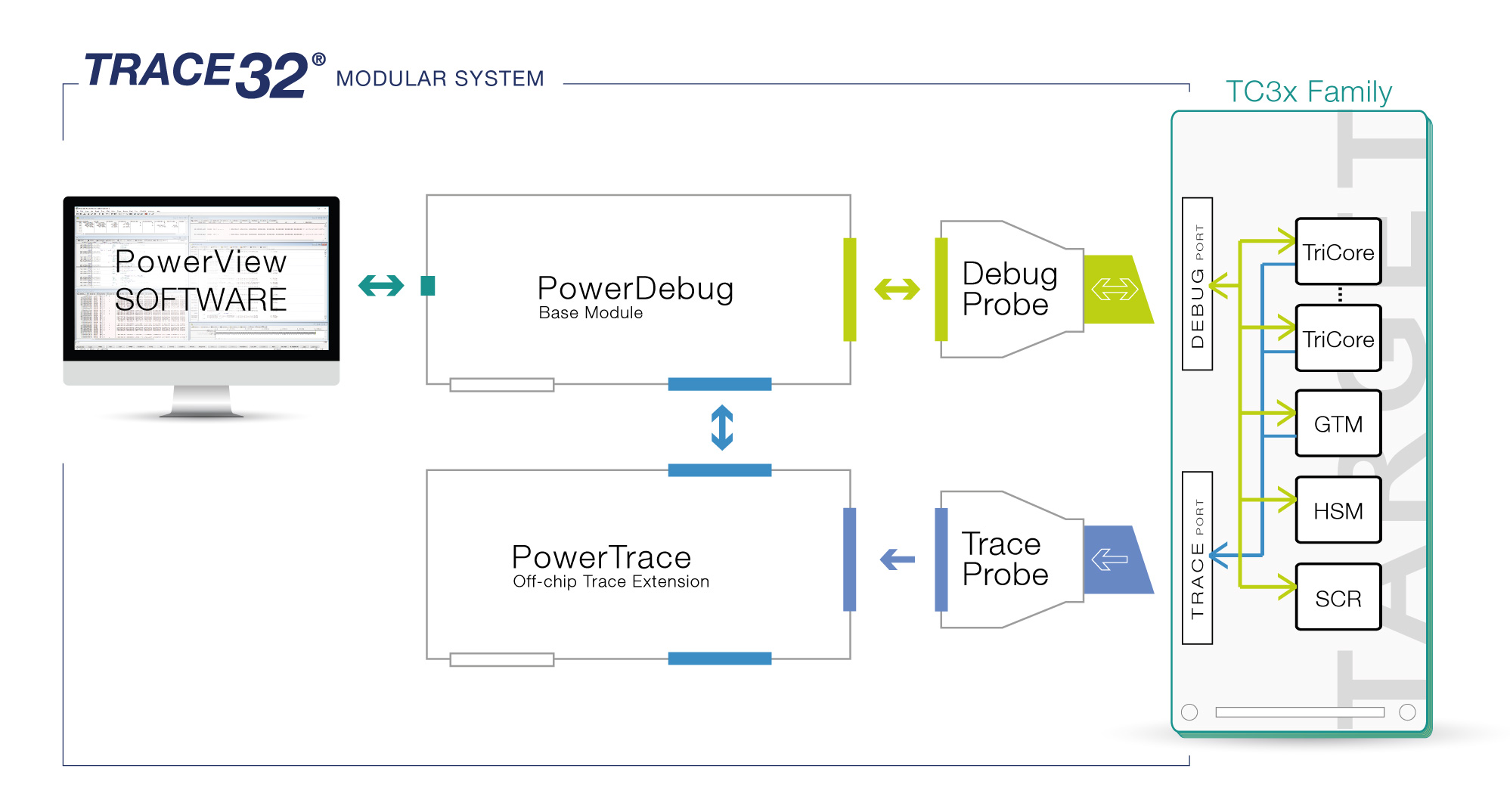

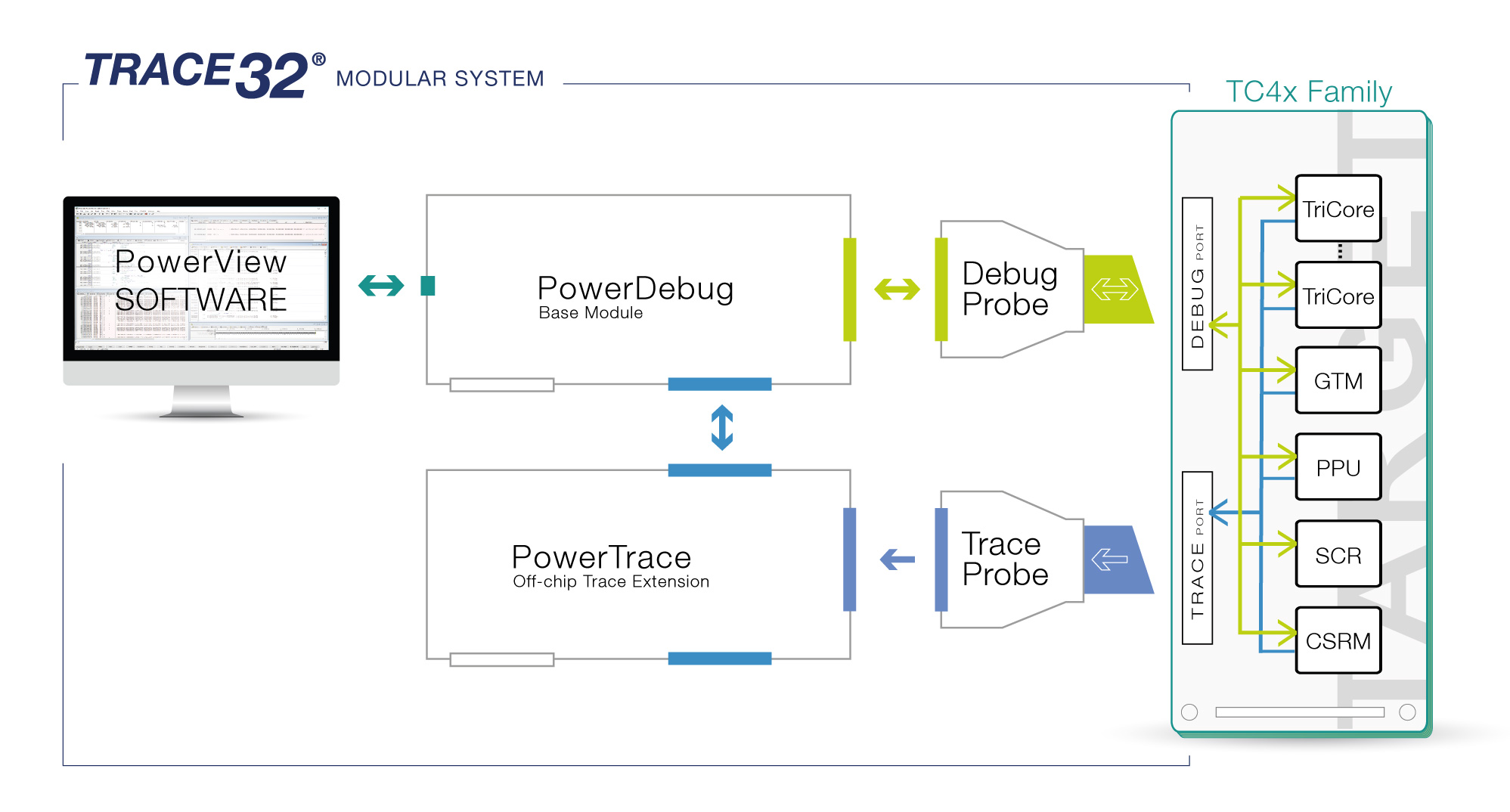

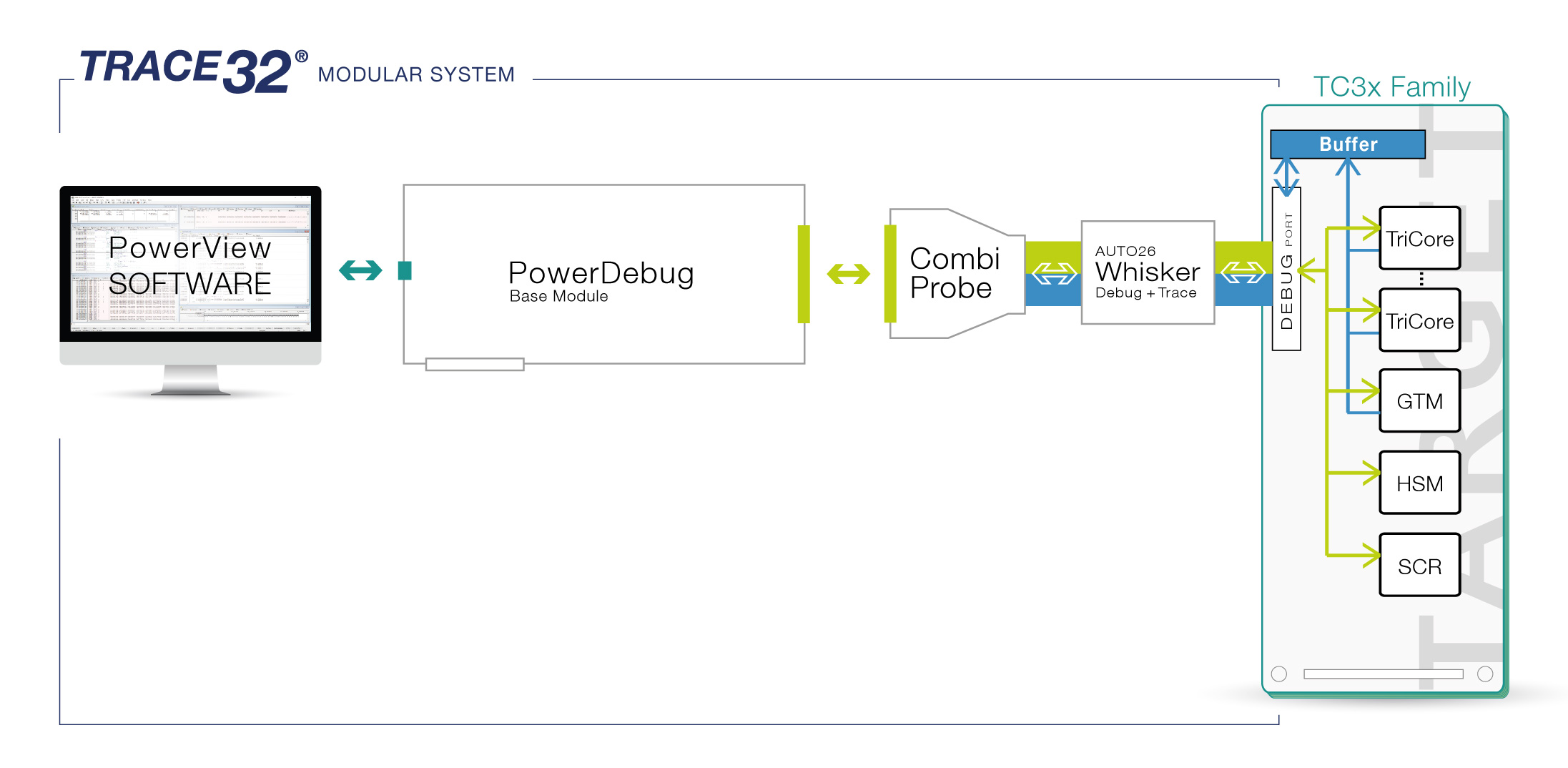

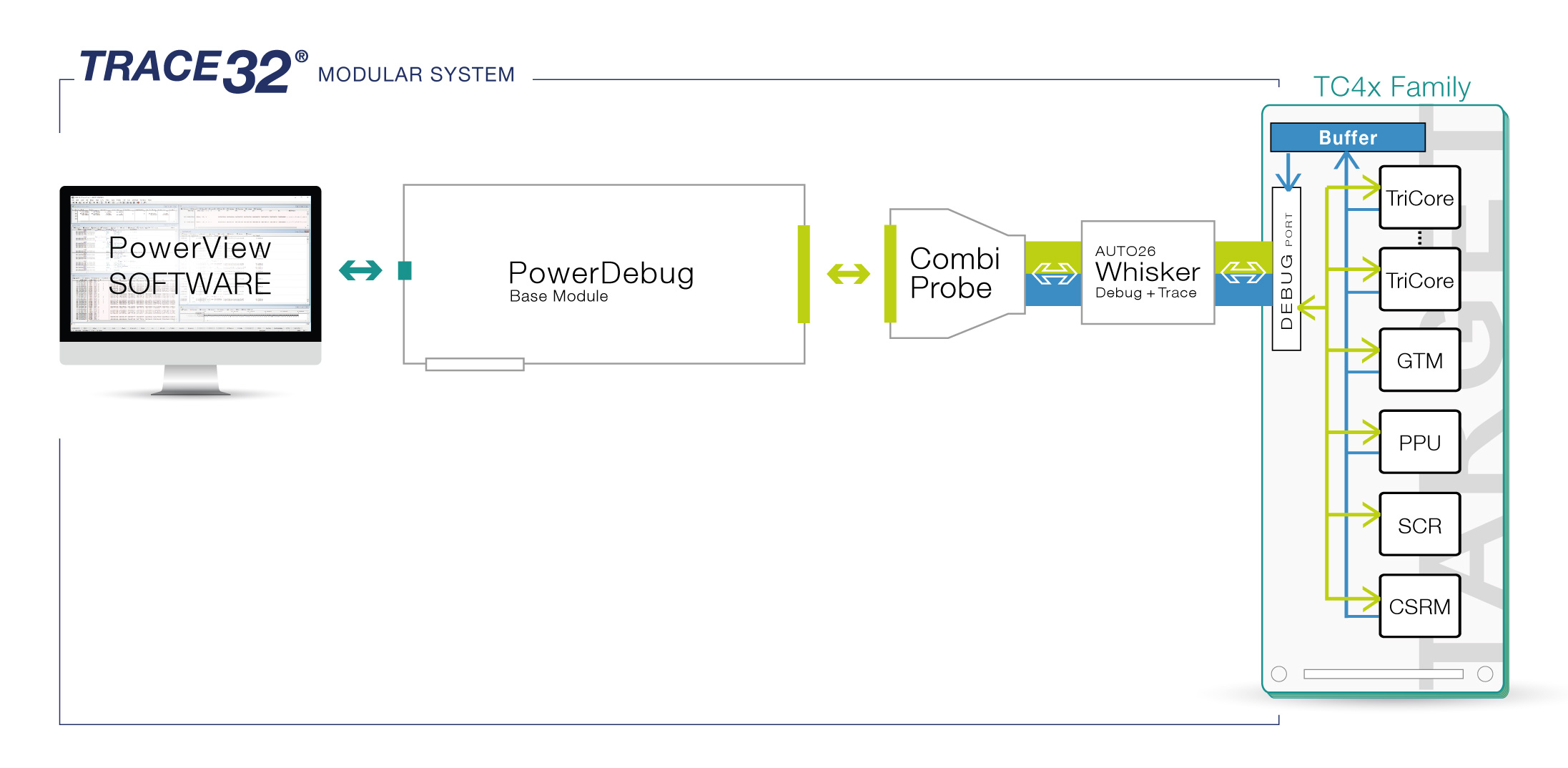

By combining elements of a RISC processor core, a microcontroller, and a DSP into a single MCU, TriCore has become the de-facto processor for modern automotive systems. A powerful architecture with multiple cores and a well-defined debug interface is allowing TriCore expand its reach to include Secure Systems, Industrial Control, Artificial Intelligence, and Machine Learning. TRACE32 offers a number of debug and trace solutions for all TriCore devices.

Supported Families

AURIX: TC4x / TC3xx / TC2xx, TC1xxx: AUDO / industrial / ...

Which TriCore are you using?

Check out our catalogue of predefined solutions and find the ideal toolset for your project.

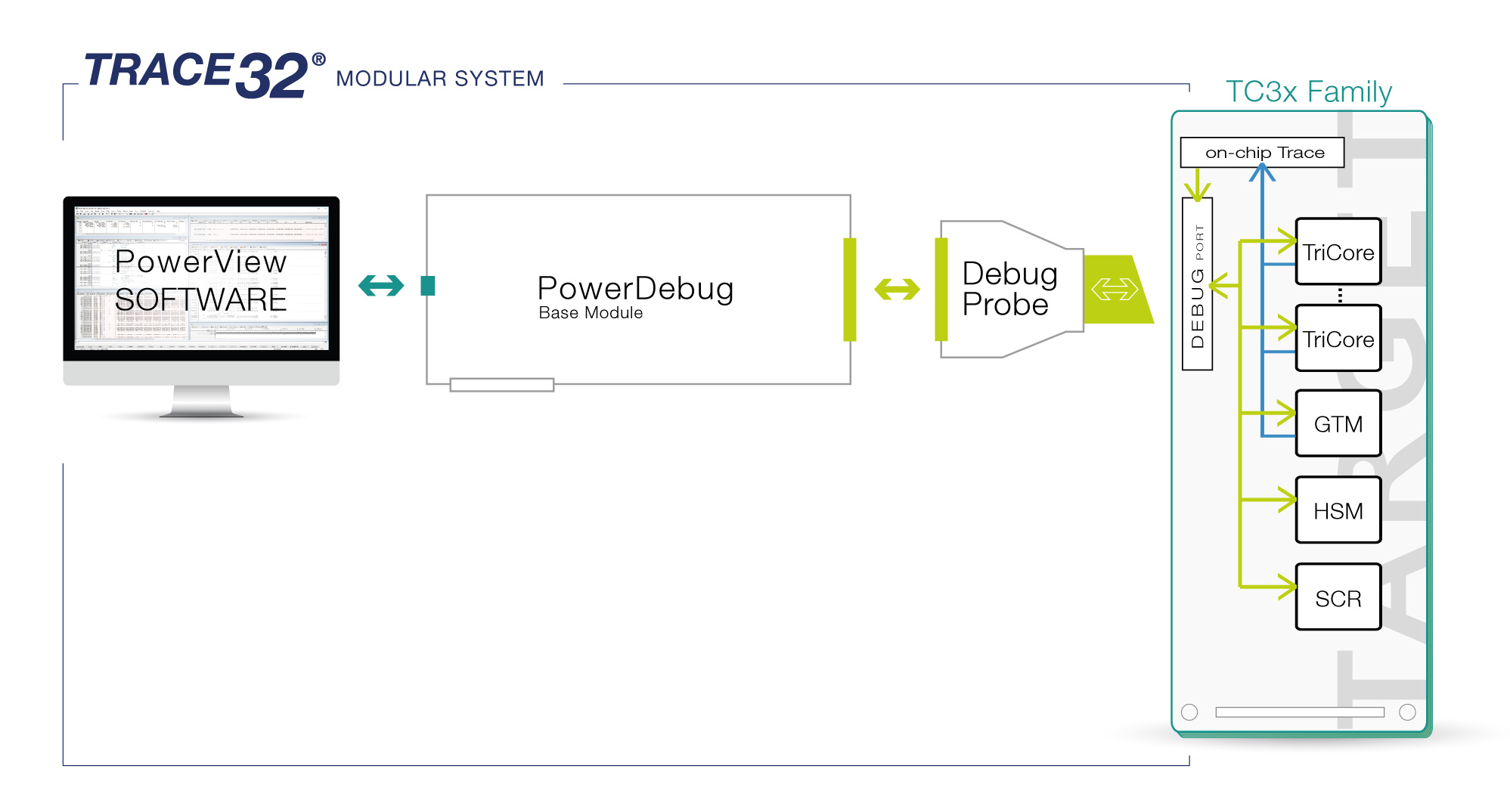

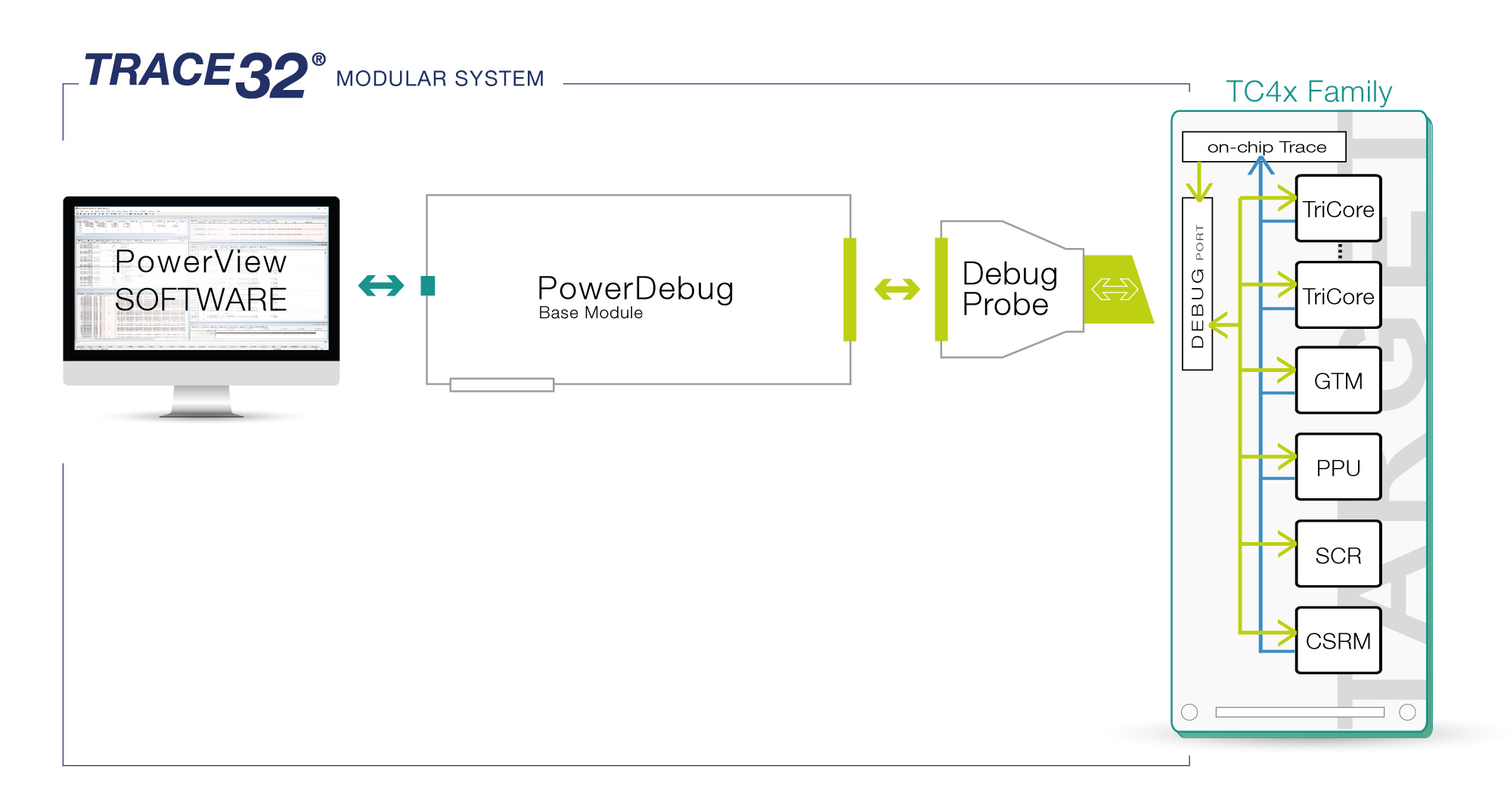

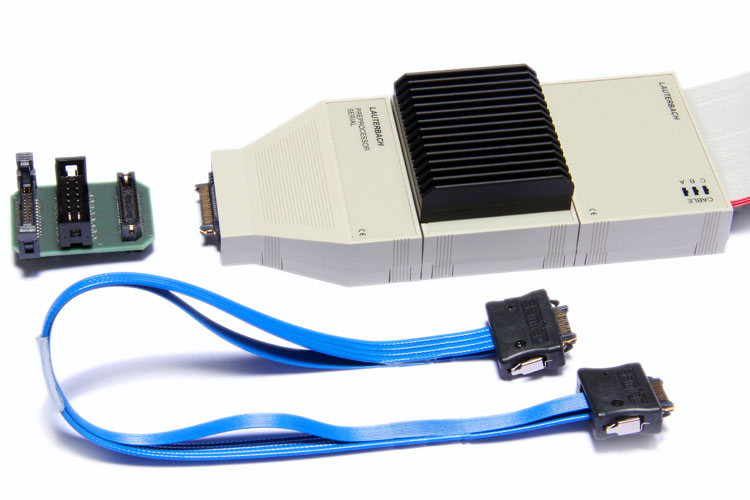

Powerful Trace Tools

TriCore Emulation Devices are capable of providing trace information, such as program flow or access cycles. This data is generated non-intrusively by the TriCore device and can be sent to local (on-chip) trace memory or streamed off-chip via a high-speed serial trace port; either Aurora Gigabit Trace (AGBT) or Serial Gigabit Trace (SGBT). As well as providing trace for the main TriCore core(s), trace is also available from the subsidiary cores GTM, PPU, and PCP and selected on-chip engines and controllers. This trace information is timestamped and provides incredible levels of detail for analysis of all aspects of your target system.

Which TriCore are you using?

Check out our catalogue of predefined solutions and find the ideal toolset for your project.

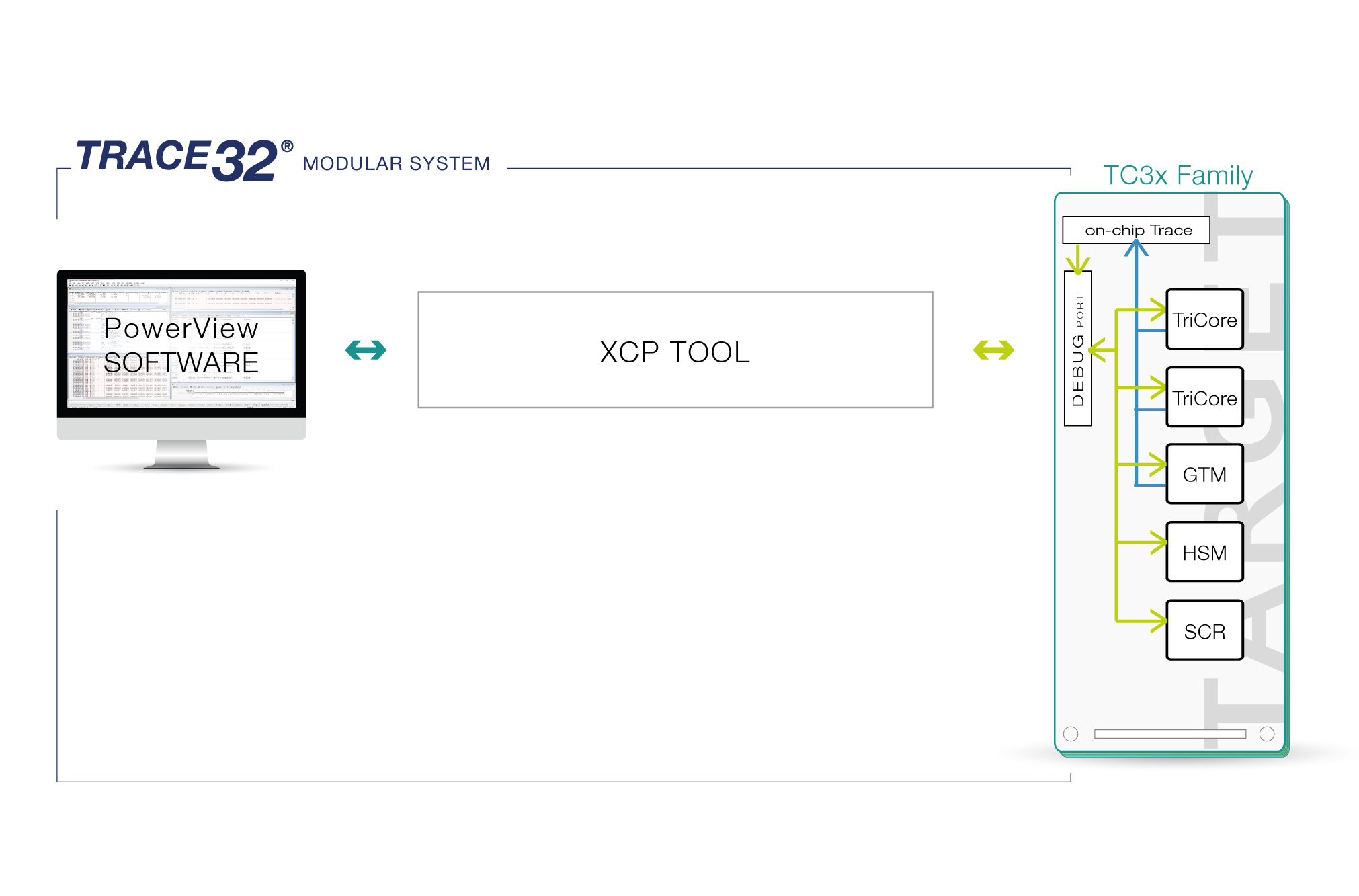

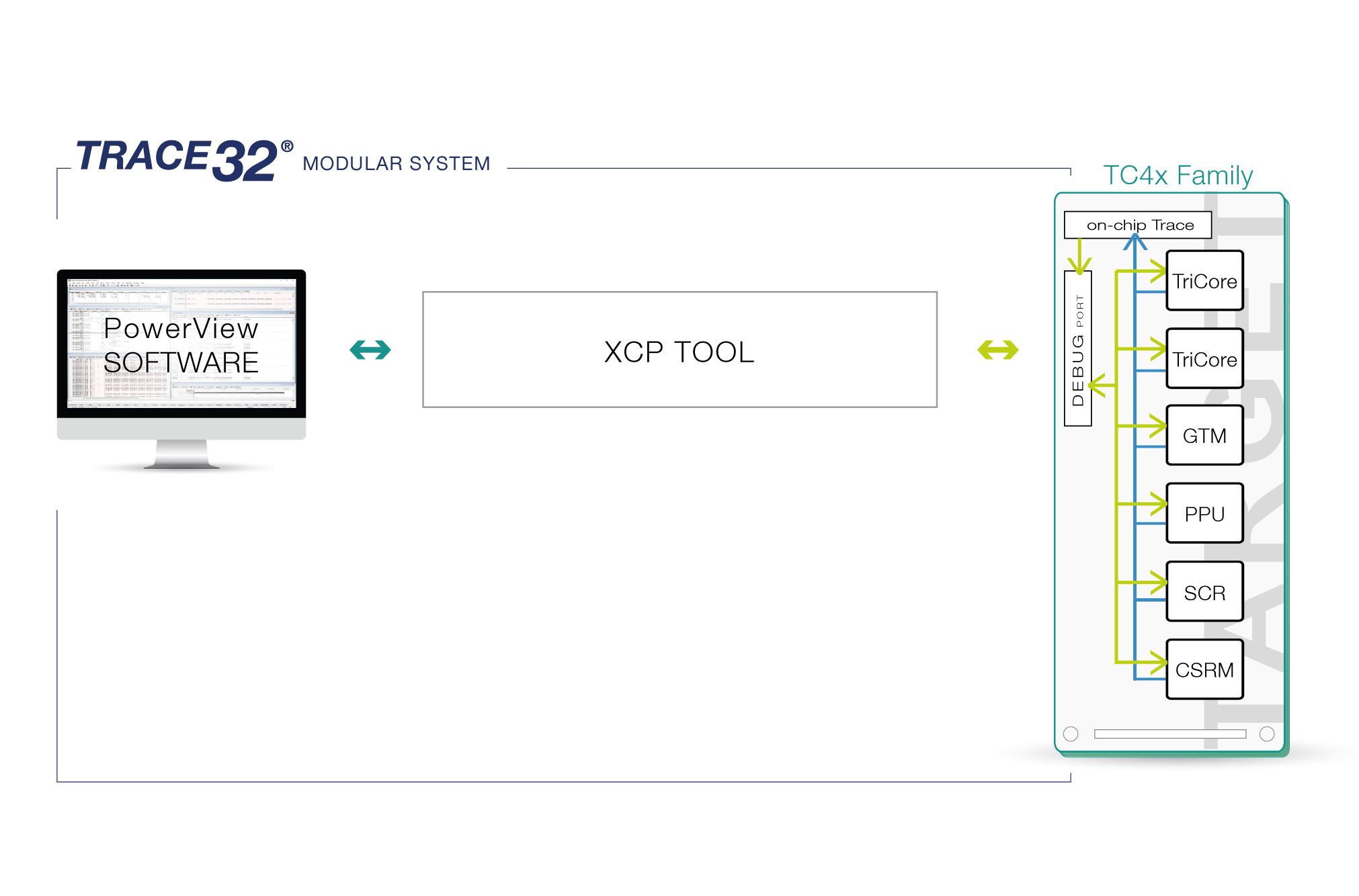

Get Ready Before Your Silicon is

You have a wide choice of debug options for your TriCore based system. Some of these may include software only debuggers, such as those outlined here.

Software licenses require a working Reprise License Manager or access to a cloud-based license server. More information about this can be found here.

3rd Party Tools Supported for TriCore

The following features are available for all architectures supported by TRACE32. Please contact us if your device or tool is not listed here; support is often already on its way.