Product Catalogue

Find TRACE32 product

Supports Xtensa Cores from Tensilica. Core trace decoding for TRAX included. Please add the base serial number of your existing debug cable or CombiProbe to your order.

supports Xtensa Cores from Tensilica via an ARM JTAG interface core trace decoding for TRAX (Trace RAM within core logic) included includes software for Windows, Linux and MacOSX requires Power Debug Module IDC20A debug cable requires LA-3763 if 14 pin JTAG (Xtensa) connector is used

Preprocessor for CoreSight Real-Time Trace for Xtensa Variable threshold level and termination voltage, AUTOFOCUS self calibration technology, Voltage: 1.2 to 3.3V - else contact support Traceport: 1-32bit Bandwidth: 9.6 Gbps (300MHz clock speed, DDR) Connector: 2x38 pin mictor connector Requires PowerTrace Version 6 or higher or PowerTrace II / III

Supported for CoreSight Xtensa if applied to a PowerTrace Serial please add the serial number of the PowerTrace Serial to your order

Supports CoreSight Trace for Xtensa Please add the base serial number of your existing debug cable to your order.

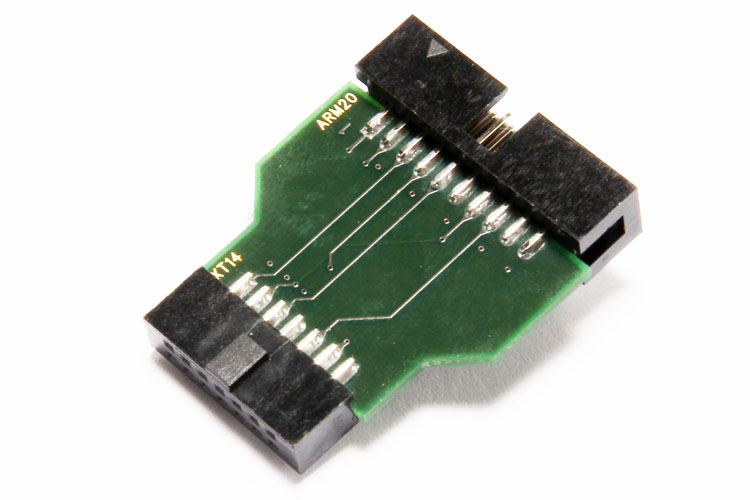

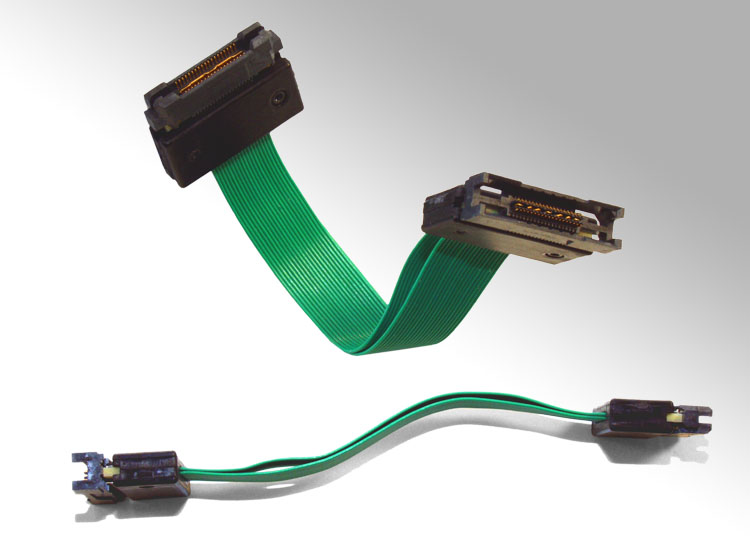

allows to connect LA-3762 to boards designed for LA-3760 Former name: Converter ARM20 to XTENSA14

Supports Xtensa Cores from Tensilica via an ARM JTAG interface Core trace decoding for TRAX (Trace RAM within core logic) included IDC20A debug cable, which supports 5-pin standard JTAG, cJTAG (IEEE 1149.7) and serial Wire Debug (SWD), (0.4V - 5V) Includes software for Windows, Linux and macOS Requires PowerDebug module Requires LA-3763 if 14 pin JTAG (Xtensa) connector is used

supports Xtensa Cores from Tensilica includes software for Windows, Linux and MacOSX requires Power Debug Module debug cable with 14 pin connector

Serial preprocessor for CoreSight Real-Time Trace for Xtensa Includes Samtec 40-pin flex extension and software. Records up to 3 lanes with 6.25 Gbit/s per lane or 4 lane with 5.00 Gbit/s per lane. Voltage range: 0.15 to 1.25 differential Voltage. Requires PowerTrace II or PowerTrace III.

Trace license to support CoreSight Trace for Xtensa, applicable to AutoFocus II preprocessor or a PowerTrace Serial. Requires an AutoFocus II preprocessor with a base serial number of C1210xxxxxxx or higher. Please add the base serial number of your existing AutoFocus II preprocesso to your order.

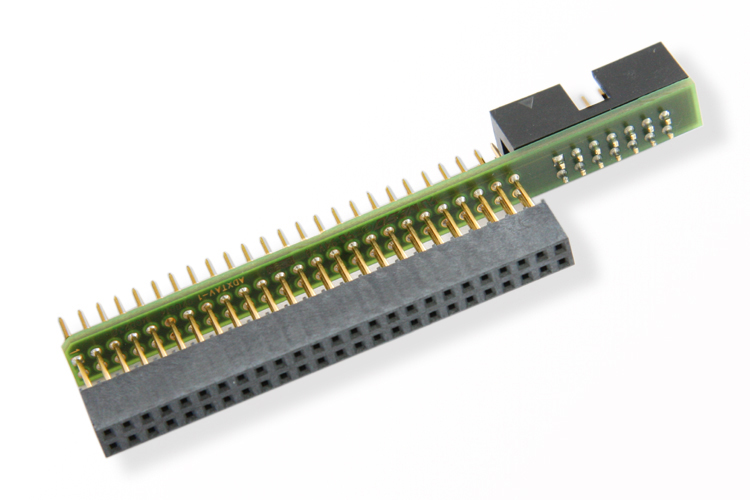

XTENSA JTAG Adapter to XTAV60 Target 14 pin to 50 pin Boards: XTAV60

Core trace decoding for Xtensa architecture For tracing Xtensa via Tessent Embedded Analytics (former UltraSoC) via USB please contact Lauterbach floating license via RLM (Reprise License Manager) Please add the RLM HostID of the license server to your order (please see our FAQ)

Trace license to support CoreSight Trace for Xtensa, applicable to AutoFocus II or serial preprocessor or a PowerTrace Serial. If the license is applied to an AutoFocus II preprocessor, the preprocessor must have a base serial number of C1210xxxxxxx or higher. Please add the base serial number of your existing AutoFocus II preprocessor, serial preprocessor or PowerTrace Serial to your order.

Parallel Preprocessor for CoreSight Real-Time Trace for Xtensa Variable threshold level and termination voltage, AUTOFOCUS self calibration technology, Voltage: 1.2 to 3.3V - else contact support Traceport: 1-32bit Bandwidth: 9.6 Gbps (300MHz clock speed, DDR) Connector: 2x38 pin mictor connector Requires PowerTrace Version 6 or PowerTrace II / III

Floating license, for connecting the TRACE32 front end for Xtensa to various 3rd party interfaces, for debugging simulators, emulators and virtual targets, as well as physical targets via USB. Supports the following interfaces: * Multi-Core Debug API (MCD) * GDB over Remote Serial Protocol (RSP) * Generic Transactor Library (GTL) (requires license LA-8983L) * Tessent Embedded Analytics via USB (requires license LA-8977L) * Intel® DCI.DbC (requires license LA-8968L). Supports the Cadence Tensilica Xtensa core architecture. For trace decoding please add license LA-9002L. For AMP multicore setups please add license LA-8902L. Floating license via RLM (Reprise License Manager). Please add the RLM HostID of the license server to your order.

License for debugging the Xtensa architecture via Tessent Embedded Analytics (former UltraSoC) USB Debug for Windows and Linux requires TRACE32 software R.2022.02 The TRACE32 software must be specially adapted from Lauterbach for each chip. Please contact the Lauterbach development departement before ordering. floating license via RLM (Reprise License Manager) Please add the RLM HostID of the license server to your order (please see our FAQ)

Trace recorder for serial high-speed ports with 4 Gigabyte trace memory for CoreSight Real-Time Trace for Xtensa Records up to 8 lanes with 12.5 Gbit/s per lane (more with opt. Prepro.) Voltage range: 0.15 to 1.25 differential voltage. Optional Mixed-Signal Probe with LA-2500. Requires accessory kit LA-3521 or LA-3522. Requires PowerDebug X50, PowerDebug PRO, or PowerDebug II. Requires PC with USB 3 or Gigabit Ethernet, 4 GB RAM min, and 64-bit OS.

Trace recorder for serial high-speed ports with 8 Gigabyte trace memory for CoreSight Real-Time Trace for Xtensa Records up to 8 lanes with 12.5 Gbit/s per lane (more with opt. Prepro.) Voltage range: 0.15 to 1.25 differential voltage. Optional Mixed-Signal Probe with LA-2500. Requires accessory kit LA-3521 or LA-3522. Requires PowerDebug X50, PowerDebug PRO, or PowerDebug II. Requires PC with USB 3 or Gigabit Ethernet, 4 GB RAM min, and 64-bit OS.

License for debugging the Xtensa architecture via Generic Transactor Library for Windows and Linux for RTL emulation or RTL simulation requires that EDA partner supports GTL interface floating license via RLM (Reprise License Manager) Please add the RLM HostID of the license server to your order (please see our FAQ)